20b-linear 100MS/s DAC

View more →

14b 30kS/s serial ADC

View more →

15b 4kS/s serial ADC

View more →

12b 1MS/s serial ADC

View more →

14b 560kS/s pipeline ADC

View more →

LiDAR: optical receiver amplifier

View more →

Wireless 5G base station transceiver

View more →

Universally reconfigurable 14-bit capacitive sensor interface

View more →

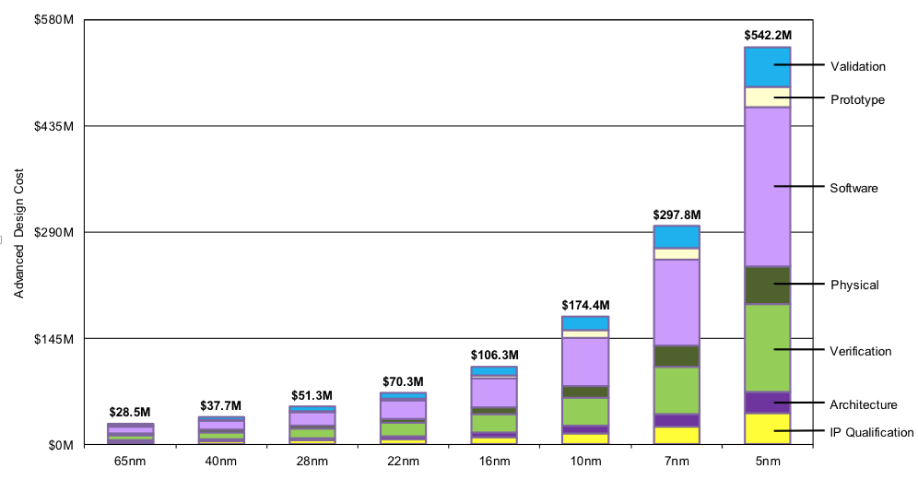

Exponential rising of ASIC R&D cost as semiconductor chips are approaching 5nm technology node

Mark LaPedus: Big Trouble at 3nm (21.June 2018)

“Design costs are also a problem. Generally, IC design costs have jumped from $51.3 million for a 28nm planar CMOS device to $297.8 million for a 7nm FinFET chip and $542.2 million for 5nm FinFET, according to IBS. But at 3nm, IC design costs range from a staggering $500 million to $1.5 billion, according to IBS.For that reason, customers likely will stay at certain nodes longer, such as 22nm/16nm/14nm and 7nm, before even thinking about switching to 3nm. Some may never move to 3nm. And if or when gate-all-around appears, it may get pushed out beyond its target date of 2021.Design costs are also a problem. Generally, IC design costs have jumped from $51.3 million for a 28nm planar CMOS device to $297.8 million for a 7nm FinFET chip and $542.2 million for 5nm FinFET, according to IBS. But at 3nm, IC design costs range from a staggering $500 million to $1.5 billion, according to IBS.For that reason, customers likely will stay at certain nodes longer, such as 22nm/16nm/14nm and 7nm, before even thinking about switching to 3nm. Some may never move to 3nm. And if or when gate-all-around appears, it may get pushed out beyond its target date of 2021.”